# 4.5 V to 60 V Input, 6 A Synchronous Buck Regulator

# **DESCRIPTION**

The SiC462 is a synchronous buck regulator with integrated high-side and low-side power MOSFETs. Its power stage is capable of supplying 6 A continuous current at up to 1 MHz switching frequency. This regulator produces an adjustable output voltage down to 0.8 V from 4.5 V to 60 V input rail to accommodate a variety of applications, including computing, consumer electronics, telecom, and industrial.

SiC462's architecture delivers ultra-fast transient response with minimum output capacitance and tight ripple regulation at very light load. The device is stable with any capacitor and no external ESR network is required for loop stability. The device also incorporates a power saving scheme that significantly increases light load efficiency.

The regulators integrates a full protection feature set, including output overvoltage protection (OVP), output undervoltage protection (UVP) and thermal shutdown (OTP). It also has UVLO for input rail and a user programmable soft start.

The SiC462 is available in lead (Pb)-free power enhanced MLP55-27L package.

# **FEATURES**

- Single supply operation from 4.5 V to 60 V input voltage

- Adjustable output voltage down to 0.8 V

- 6 A continuous output current

- Selectable switching frequency from 100 kHz to 1 MHz with an external resistor

- 95 % peak efficiency

- Ultra-fast transient response

- · Optional power saving mode

- < 10 µA shutdown current

- < 250 µA operating current when enabled but not switching

- Cycle-by-cycle current limit

- Output overvoltage protection

- Output undervoltage protection

- · Output voltage tracking and sequencing

- -40 °C to +125 °C operating junction temperature

#### **APPLICATIONS**

- POLs for telecom

- · Industrial and automation

- · Industrial computing

- Consumer electronics

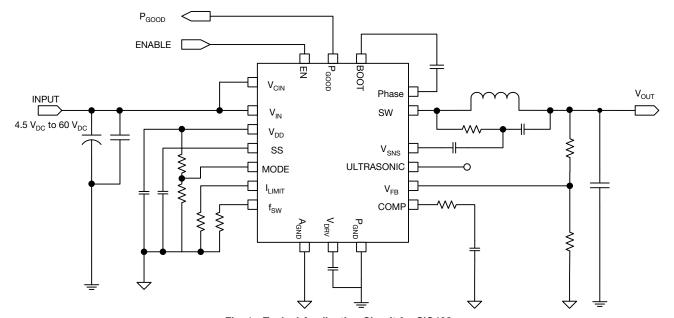

# TYPICAL APPLICATION CIRCUIT AND PACKAGE OPTIONS

Fig. 1 - Typical Application Circuit for SiC462

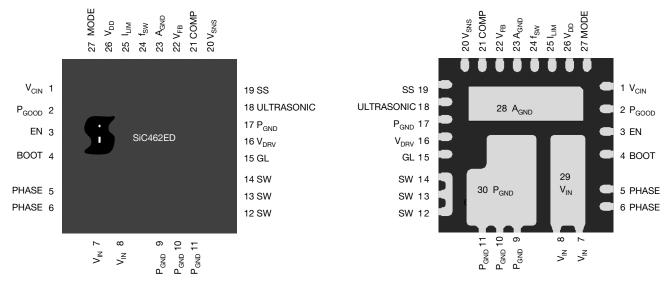

# **PIN CONFIGURATION**

Fig. 2 - SiC462 Pin Configuration

| PIN DESCRIPTION   |                    |                                                                                                                                                                                                                      |  |  |  |

|-------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NUMBER        | SYMBOL             | DESCRIPTION                                                                                                                                                                                                          |  |  |  |

| 1                 | $V_{CIN}$          | Supply voltage for internal logic circuitry                                                                                                                                                                          |  |  |  |

| 2                 | P <sub>GOOD</sub>  | Open-drain power good indicator - high impedance indicates power is good. An external pull-up resistor is required                                                                                                   |  |  |  |

| 3                 | EN                 | Enable pin                                                                                                                                                                                                           |  |  |  |

| 4                 | BOOT               | High-side driver bootstrap voltage                                                                                                                                                                                   |  |  |  |

| 5, 6              | PHASE              | Return path of high-side gate driver                                                                                                                                                                                 |  |  |  |

| 7, 8, 29          | V <sub>IN</sub>    | Power stage input voltage. Drain of high-side MOSFET                                                                                                                                                                 |  |  |  |

| 9, 10, 11, 17, 30 | $P_{GND}$          | Power ground                                                                                                                                                                                                         |  |  |  |

| 12, 13, 14        | SW                 | Power stage switch node                                                                                                                                                                                              |  |  |  |

| 15                | GL                 | Low-side MOSFET gate signal                                                                                                                                                                                          |  |  |  |

| 16                | V <sub>DRV</sub>   | Supply voltage for internal gate driver. When using the internal LDO as a bias power supply, $V_{DD}$ is the LDO output. Connect a 1 $\mu$ F decoupling capacitor to $A_{GND}$                                       |  |  |  |

| 18                | ULTRASONIC         | Float to disable ultrasonic mode, connect to $V_{DD}$ to enable. Depending on the operation mode set by the MODE pin, power save mode or forced continuous mode will be enabled when the ultrasonic mode is disabled |  |  |  |

| 19                | SS                 | Set the soft start ramp by connecting a capacitor to A <sub>GND</sub> . An internal current source will charge the capacitor                                                                                         |  |  |  |

| 20                | V <sub>SNS</sub>   | Power inductor signal feedback pin for system stability compensation                                                                                                                                                 |  |  |  |

| 21                | COMP               | Output of the internal error amplifier. The feedback loop compensation network is connected from this pin to the V <sub>FB</sub> pin                                                                                 |  |  |  |

| 22                | V <sub>FB</sub>    | Feedback input for switching regulator used to program the output voltage - connect to an external resistor divider from V <sub>OUT</sub> to A <sub>GND</sub>                                                        |  |  |  |

| 23                | A <sub>GND</sub>   | Analog ground                                                                                                                                                                                                        |  |  |  |

| 24                | f <sub>SW</sub>    | Set the on-time by connecting a resistor to A <sub>GND</sub>                                                                                                                                                         |  |  |  |

| 25                | I <sub>LIMIT</sub> | Set the current limit by connecting a resistor to A <sub>GND</sub>                                                                                                                                                   |  |  |  |

| 26                | $V_{DD}$           | Bias supply for the IC. V <sub>DD</sub> is an LDO output, connect a 1 μF decoupling capacitor to A <sub>GND</sub>                                                                                                    |  |  |  |

| 27                | MODE               | Use MODE to set various operation modes. See specification table                                                                                                                                                     |  |  |  |

|                   |                    |                                                                                                                                                                                                                      |  |  |  |

| ORDERING INFORMATION |                            |              |  |  |

|----------------------|----------------------------|--------------|--|--|

| PART NUMBER          | PACKAGE                    | MARKING CODE |  |  |

| SiC462ED-T1-GE3      | PowerPAK® MLP55-27L SiC462 |              |  |  |

| SiC462EVB            | PEVB Reference board       |              |  |  |

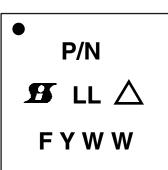

# PART MARKING INFORMATION

= pin 1 indicator

P/N = part number code

**B** = Siliconix logo

$\triangle$  = ESD symbol

F = assembly factory code

Y = year code

WW = week code

LL = lot code

| ABSOLUTE MAXIMUM RATINGS (TA                | = 25 °C, unless otherwise noted)  |                                               |      |

|---------------------------------------------|-----------------------------------|-----------------------------------------------|------|

| ELECTRICAL PARAMETER                        | CONDITIONS                        | LIMITS                                        | UNIT |

| EN, V <sub>CIN</sub> , V <sub>IN</sub>      | Reference to P <sub>GND</sub>     | -0.3 to +63                                   |      |

| SW / PHASE                                  | Reference to P <sub>GND</sub>     | -0.3 to +66                                   | 1    |

| SW / PHASE (AC)                             | 100 ns                            | -4 to +72                                     | V    |

| BOOT                                        |                                   | -0.3 to V <sub>PHASE</sub> + V <sub>DRV</sub> | V    |

| A <sub>GND</sub> to P <sub>GND</sub>        |                                   | -0.3 to +0.3                                  |      |

| All other pins                              | Reference to A <sub>GND</sub>     | -0.3 to V <sub>DD</sub> + 0.3                 |      |

| Temperature                                 |                                   |                                               |      |

| Junction temperature                        | T <sub>J</sub> -40 to +15         |                                               | °C   |

| Storage temperature                         | T <sub>STG</sub>                  | -65 to +150                                   |      |

| Power Dissipation                           |                                   |                                               |      |

| Thermal resistance from junction to ambient |                                   | 2                                             | °C/W |

| Thermal resistance from junction to case    |                                   | 12                                            | ]    |

| ESD Protection                              |                                   |                                               |      |

| Electrostatic discharge protection          | Human body model, JESD22-A114     | 2000                                          | V    |

| Liectiostatic discharge protection          | Charged device model, JESD22-A101 | 750                                           | ]    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

| <b>RECOMMENDED OPERATING CONDITIONS</b> (all voltages referenced to GND = 0 V) |      |             |                       |      |  |

|--------------------------------------------------------------------------------|------|-------------|-----------------------|------|--|

| PARAMETER                                                                      | MIN. | TYP.        | MAX.                  | UNIT |  |

| Control input voltage (V <sub>CIN</sub> ) (1)                                  | 4.5  | -           | 60                    |      |  |

| Enable (EN)                                                                    | 5    | -           | 60                    |      |  |

| Bias supply (V <sub>DD</sub> )                                                 | 4.75 | 5           | 5.25                  | V    |  |

| Drive supply voltage (V <sub>DRV</sub> )                                       | 4.75 | 5.3         | 5.5                   |      |  |

| Output voltage (V <sub>OUT</sub> )                                             | 0.8  | -           | 0.8 x V <sub>IN</sub> |      |  |

| Temperature                                                                    |      |             |                       |      |  |

| Recommended ambient temperature                                                |      | -40 to +105 |                       | °C   |  |

| Operating junction temperature                                                 |      | -40 to +125 |                       | -0   |  |

# Note

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

<sup>(1)</sup> For input voltages below 5 V, provide a separate supply to V<sub>CIN</sub> of at least 5 V to prevent the internal V<sub>DD</sub> rail UVLO from triggering.

|                                    |                                | $_{\rm S}$ V, $_{\rm T_J}$ = -40 °C to +125 °C, unless of                                                                                    | 1            |      |                        | ı     |

|------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------------------------|-------|

| PARAMETER                          | SYMBOL                         | TEST CONDITIONS                                                                                                                              | MIN.         | TYP. | MAX.                   | UNIT  |

| Power Supplies                     |                                |                                                                                                                                              |              |      |                        |       |

| LDO output                         | $V_{DD}$                       | $V_{IN}/V_{CIN} = 7 \text{ V to } 55 \text{ V}$                                                                                              | -            | 5    | -                      | V     |

| V <sub>DD</sub> UVLO threshold     | $V_{DD\_UVLO}$                 | -                                                                                                                                            | -            | 4.25 | -                      | v     |

| V <sub>DD</sub> UVLO hysteresis    | V <sub>DD_UVLO_HYST</sub>      |                                                                                                                                              | -            | 300  | -                      | mV    |

| Driver voltage                     | V <sub>DRV</sub>               | $V_{IN}/V_{CIN} = 7 \text{ V to } 55 \text{ V}$                                                                                              | _            | 5.3  | -                      |       |

| V <sub>DRV</sub> UVLO threshold    | V <sub>DRV_UVLO</sub>          | IIV OIIV                                                                                                                                     | -            | 4.25 | -                      | V     |

| V <sub>DRV</sub> UVLO hysteresis   | V <sub>DRV_UVLO_HYST</sub>     |                                                                                                                                              | -            | 300  | -                      | mV    |

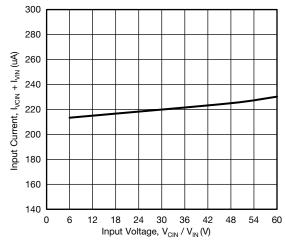

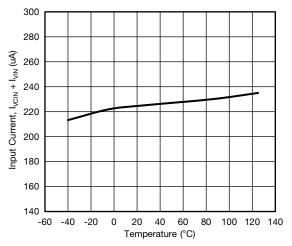

| Input current                      | IV <sub>IN</sub>               | T <sub>J</sub> = 25 °C, non-switching,<br>no load, V <sub>FB</sub> > 0.8 V                                                                   | _            | -    | 250                    | μА    |

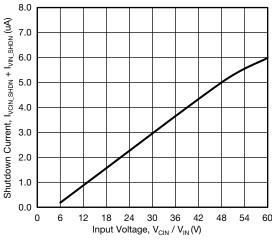

| Shutdown current                   | IV <sub>IN_SHDN</sub>          | EN = 0 V                                                                                                                                     | _            | 5    | 10                     | μΛ    |

| Controller and Timing              | I IN SHUN                      | 214 - 0 4                                                                                                                                    |              |      | 10                     |       |

| Controller and Timing              |                                | T 25 °C                                                                                                                                      | -0.5         | l _  | 0.5                    |       |

| Feedback voltage                   | V <sub>FB</sub>                | $T_J = 25 ^{\circ}\text{C}$<br>$T_J = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}$                                                        | -0.5         | -    | 1                      | %     |

| V <sub>FB</sub> input bias current | I <sub>FB</sub>                |                                                                                                                                              | -            | 2    | -                      | nA    |

| Transconductance                   | 9 <sub>m</sub>                 |                                                                                                                                              | -            | 0.3  | -                      | mS    |

| COMP source current                | I <sub>COMP_SOURCE</sub>       |                                                                                                                                              | -            | 20   | -                      |       |

| COMP sink current                  | I <sub>COMP_SINK</sub>         |                                                                                                                                              | -            | 20   | -                      | μA    |

| On-time                            | t <sub>ON</sub>                |                                                                                                                                              | -            | 100  | -                      | ns    |

| t <sub>ON</sub> accuracy           | ton accuracy                   |                                                                                                                                              | _            | 10   | -                      | %     |

| On-time range                      | ton range                      |                                                                                                                                              | 100          | -    | 8000                   | ns    |

|                                    | *ON_RANGE                      | Ultrasonic mode enabled                                                                                                                      | 20           | -    | 1000                   |       |

| Frequency range                    | f <sub>kHz</sub>               | Ultrasonic mode disabled                                                                                                                     | -            | -    | 1000                   | kHz   |

| Minimum off-time                   |                                | Olli asonic mode disabled                                                                                                                    |              |      |                        |       |

|                                    | t <sub>OFF_min</sub> .         |                                                                                                                                              | -            | 250  | -                      | ns    |

| Soft start current                 | I <sub>SS</sub>                | 140                                                                                                                                          | -            | 5    | -                      | μA    |

| Soft start voltage                 | $V_{SS}$                       | When V <sub>OUT</sub> reaches regulation                                                                                                     | _            | 1.5  | -                      | V     |

| Power MOSFETs                      | 1                              |                                                                                                                                              |              | 1    | 1                      |       |

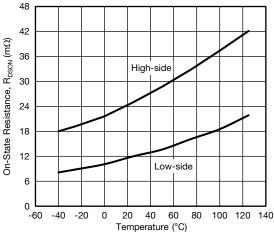

| High-side on resistance            | R <sub>ON_HS</sub>             | $V_{GS} = 5.3 \text{ V}$                                                                                                                     | -            | 25   | -                      | mΩ    |

| Low-side on resistance             | R <sub>ON_LS</sub>             | VGS = 0.0 V                                                                                                                                  | -            | 12   | -                      | 11122 |

| Fault Protections                  |                                |                                                                                                                                              |              |      |                        |       |

| Over current limit                 | I <sub>OCP</sub>               | Output current (assume 2 A p-p ripple current with 6 A output current),  R <sub>LIM</sub> set for 8 A typ., T <sub>J</sub> = 0 °C to +125 °C | -            | 8    | -                      | А     |

| Current limit setting range        | I <sub>LIM RANGE</sub>         | R <sub>LIM</sub>                                                                                                                             | 3            | -    | 8                      |       |

| Current limit accuracy             | ILIM ACCURACY                  | 1 % resistor used for R <sub>LIM</sub>                                                                                                       | _            | 20   | -                      |       |

| Output OVP threshold               | OVP                            |                                                                                                                                              | -            | 20   | -                      | %     |

| Output UVP threshold               | UVP                            | V <sub>FB</sub> with respect to 0.8 V reference                                                                                              | _            | -80  | -                      | ,,,   |

| Catpat CVI timedilola              | OTPR                           | Rising temperature                                                                                                                           | _            | 150  | -                      |       |

| Over temperature protection        | OTP <sub>HYST</sub>            | Hysteresis                                                                                                                                   | _            | 35   | _                      | °C    |

| Power Good                         | OTFHYST                        | Hysteresis                                                                                                                                   | _            | 33   | _                      |       |

| rower dood                         | V                              | V riging shave 0.0 V f                                                                                                                       | l            | 00   | l                      |       |

| Power good output threshold        | V <sub>FB_RISING_VTH_OV</sub>  | V <sub>FB</sub> rising above 0.8 V reference                                                                                                 | -            | 20   | -                      | %     |

|                                    | V <sub>FB_FALLING_VTH_UV</sub> | V <sub>FB</sub> falling below 0.8 V reference                                                                                                | -            | -10  | -                      |       |

| Power good hysteresis              | P <sub>GOOD_HYST</sub>         |                                                                                                                                              | -            | 40   | -                      | mV    |

| Power good on resistance           | R <sub>ON_PGOOD</sub>          |                                                                                                                                              | -            | 10   | -                      | Ω     |

| Power good delay time              | t <sub>DLY_PGOOD</sub>         |                                                                                                                                              | -            | 25   | -                      | μs    |

| EN / MODE / Ultrasonic Threshold   |                                |                                                                                                                                              |              |      |                        |       |

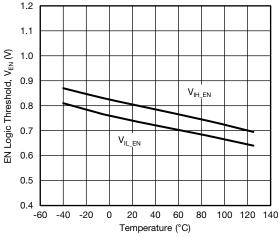

| EN logic high level                | $V_{EN\_H}$                    |                                                                                                                                              | 1.4          | -    | -                      | 17    |

| EN logic low level                 | V <sub>EN_L</sub>              |                                                                                                                                              | -            | -    | 0.4                    | V     |

| EN pull down resistance            | R <sub>EN</sub>                |                                                                                                                                              | -            | 5    | -                      | ΜΩ    |

| Ultrasonic mode high Level         | U <sub>HIGH</sub>              |                                                                                                                                              | 2            | -    | -                      |       |

| Ultrasonic mode low level          | U <sub>LOW</sub>               |                                                                                                                                              |              | _    | 0.8                    | V     |

| Mode pull up current               | i                              |                                                                                                                                              | <del>-</del> | 5    |                        |       |

|                                    | I <sub>MODE</sub>              | Chin made enabled V V Director                                                                                                               | -            | _    | - 0.7                  | μΑ    |

| MODE1                              |                                | Skip mode enabled, V <sub>DD</sub> , V <sub>DRV</sub> Pre-reg on                                                                             | 0            | -    | 0.7                    | 1     |

| N/( )  11-2                        | 1                              | Skip mode disabled, V <sub>DD</sub> , V <sub>DRV</sub> Pre-reg on                                                                            | 1.3          | -    | 1.7                    | ]     |

| MODE2                              |                                | Skip mode disabled, V <sub>DRV</sub> Pre-reg off,                                                                                            | 23           | _    | 27                     | V     |

| MODE3  MODE4                       |                                |                                                                                                                                              | 2.3          | -    | 2.7<br>V <sub>DD</sub> | V     |

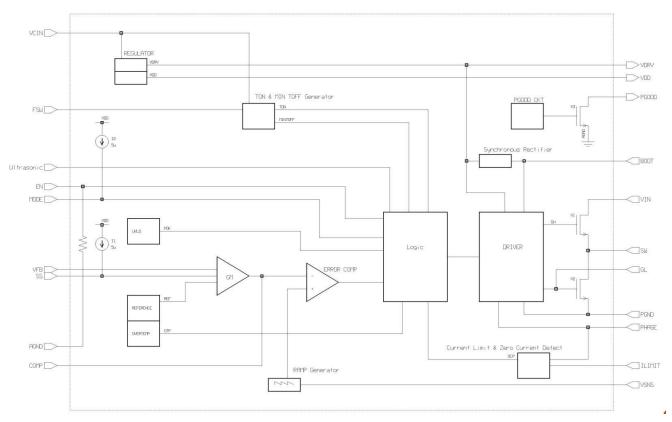

# **FUNCTIONAL BLOCK DIAGRAM**

Fig. 3 - SiC462 Functional Block Diagram

# **OPERATIONAL DESCRIPTION**

#### **Device Overview**

SiC462 is a high-efficiency synchronous buck regulator capable of delivering up to 6 A continuous current. The device has programmable switching frequency of 100 kHz to 1 MHz. The control scheme delivers fast transient response and minimizes external components. A proprietary V²-COT control mechanism enables loop stability regardless of the type of output capacitor used, including low-ESR ceramic capacitors. This device also incorporates a power saving feature by enabling diode emulation mode and frequency fold back as the load decreases.

SiC462 has a full set of protection and monitoring features:

- Over current protection in pulse-by-pulse mode

- Output overvoltage protection

- Output undervoltage protection with device latch

- Over temperature protection with hysteresis

- Dedicated enable pin for easy power sequencing

- Power good open drain output

- This device is available in MLP55-32L package to deliver high power density and minimize PCB area.

# **Power Stage**

SiC462 integrates a high-performance power stage with a  $25\,\mathrm{m}\Omega$  n-channel high side MOSFET and a  $12\,\mathrm{m}\Omega$  n-channel low side MOSFET. The MOSFETs are optimized to achieve up to 96 % efficiency.

The power input voltage  $(V_{\text{IN}})$  can go up to 60 V and down as low as 5 V for power conversion.

# **PWM Control Mechanism**

SiC462 employs a voltage - mode COT control mechanism with two voltage ( $V^2$ ) feedback loops. The switching frequency,  $f_{SW}$ , it set by an external resistor to  $A_{GND}$ ,  $R_{fsw}$ .

$$R_{fsw} = \frac{V_{OUT}}{(f_{SW} \times 190e^{-12})}$$

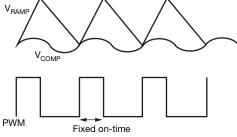

During steady-state operation, feedback voltage is compared with internal reference (0.8 V typ.) and the amplified error signal ( $V_{COMP}$ ) is generated in the internal comp node. An internally generated ramp signal and  $V_{COMP}$  are fed into a comparator. Once  $V_{RAMP}$  crosses  $V_{COMP}$ , a single shot ON-time pulse is generated for a fixed time, programmed by the external  $R_{FSW}$ . During the On-time pulse, the high side MOSFET will be turned ON. Once the ON-time pulse expires, the low side MOSFET will be turned ON after a break-before-make period. The low side MOSFET will be on for duration of minimum OFF-time pulse until  $V_{RAMP}$  crosses  $V_{COMP}$ . The cycle is then repeated.

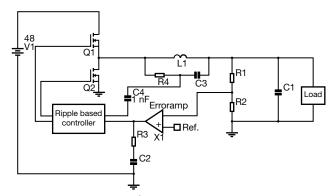

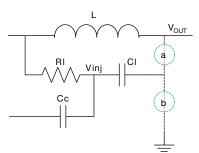

Fig. 4 illustrates the basic block diagram for V<sup>2</sup>-COT architecture. In this architecture the following is achieved:

- The reference of a basic ripple control regulator is replaced with a high again error amplifier loop

- This establishes two parallel voltage regulating feedback

paths, a fast and slow path (hence the term V<sup>2</sup> to indicate two voltage feedback paths)

- The fast path is the ripple injection which ensures rapid correction of the transient perturbation

- The slow path is the error amplifier loop which ensures the DC component of the output voltage follows the internal accurate reference voltage

Fig. 4 - V2-COT Block Diagram

For stability purposes the SiC462 requires 100 mV of ripple injection.  $C_X$ ,  $C_Y$ , and  $R_X$  are selected to achieve the desired ripple injection.

Typically  $C_y$  is chosen to be  $\geq 2$  nF to meet the internal impedance of the  $V_{SNS}$  pin.

$C_X$  is chosen to be 10 times greater than  $C_Y$ ,  $C_Y = 20$  nF.

$$R_X = (V_{IN} - V_{OUT}) \times (V_{OUT}/(V_{IN} \times f_{SW} \times C_X \times V_{RIPPLF}))$$

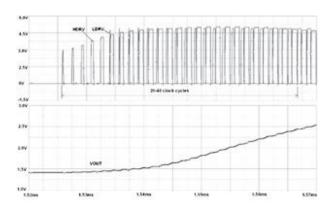

Fig. 5 demonstrates the basic operational waveforms:

Fig. 5 - V2-COT Operational Principle

Typically, the set the frequency of  $R_{COMP}$  and  $C_{COMP}$  is chosen to be around the resonance frequency of  $L_{OUT}$  and  $C_{OUT}.$

In this case, set

$$R_{COMP} \times C_{COMP} = \sqrt{L_{OUT} \times C_{OUT}}$$

For good slew rate / transient load response, pick  $C_{COMP} \leq$  1 nF,  $R_{COMP}$  can be calculated according the formula above.

# Vishay Siliconix

# Power-Save Mode, MODE Pin, and Ultrasonic Pin Operation

To improve efficiency at light-load condition, SiC462 provides a set of innovative implementations to eliminate LS re-circulating current and switching losses. The internal zero crossing detector (ZCD) monitors LX node voltage to determine when inductor current starts to flow negatively. In power saving mode, as soon as inductor valley current crosses zero, the device first deploys diode emulation mode by turning off LS FET. If load further decreases, switching frequency is further reduced proportional to load condition to save switching losses while keeping output ripple within tolerance. The switching frequency is set by the controller to maintain regulation. If the ultrasonic pin is tied to V<sub>DD</sub>, the minimum switching frequency that the regulator will drop to, as load decreases, is 20 kHz to avoid switching frequencies in the audible range. If this feature is not required this ultrasonic mode can be disabled by floating the ultrasonic pin. When the ultrasonic mode is disabled, the regulator will either operate in forced continuous mode or in a power save mode where there is no limit to the lower frequency limit. In this state, at zero load switching frequency can go as low as hundreds of Hz.

If a 5 V rail is available in the system, the customer can provide this as the  $V_{DRV}$  voltage instead of using the internal  $V_{DRV}$  regulator. This allows for power savings because power is not dissipated in the internal regulator.

The MODE pin supports several modes of operation as shown below. An internal current source is used to set the voltage on this pin using an external resistor:

| TABLE 1 - OPERATION MODES         |                                                                                                  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| MODE1<br>0 V to 0.7 V             | Power save mode enabled, V <sub>DD</sub> , V <sub>DRV</sub> Pre-reg on                           |  |  |  |  |

| MODE2<br>1.3 V to 1.7 V           | Power save mode disabled, V <sub>DD</sub> , V <sub>DRV</sub> Pre-reg on                          |  |  |  |  |

| MODE3<br>2.3 V to 2.7 V           | Power save mode disabled, $V_{DRV}$ Pre-reg off, $V_{DD}$ Pre-reg on, provide external $V_{DRV}$ |  |  |  |  |

| MODE4<br>3.3 V to V <sub>DD</sub> | Power save mode enabled, $V_{DRV}$ Pre-reg off, $V_{DD}$ Pre-reg On, provide external $V_{DRV}$  |  |  |  |  |

The mode pin is not latched to any state and can be changed on the fly.

# OUTPUT MONITORING AND PROTECTION FEATURES

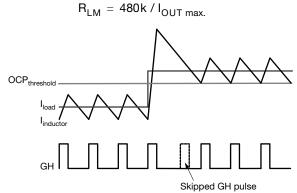

### **Output Over-Current Protection (OCP)**

SiC462 has cycle by cycle current limiting. The inductor valley current is monitored during LS FET turn-on period through  $R_{DS(on)}$  sensing. After a pre-defined blanking time, the valley current is compared with an internal threshold. If monitored current is higher than threshold, HS turn-on pulse is skipped and LS FET is kept on until the valley current returns below OCP limit.

In the severe over-current condition, cycle by cycle current limit eventually triggers output undervoltage protection (UVP) and the device will go into hiccup mode as described in the next section.

OCP is enabled immediately after  $V_{CC}$  passes UVLO level. OCP is set by an external resistor to  $A_{GND}$ ,  $R_{LIM}$ .

Fig. 6 - Over-Current Protection Illustration

# **Output Undervoltage Protection (UVP)**

UVP is implemented by monitoring output through  $V_{FB}$  pin. If the voltage level at  $V_{FB}$  goes below 0.16 V ( $V_{OUT}$  is 20% of  $V_{OUT}$  set point) for more than 25  $\mu s$ , then a UVP event is recognized and both HS and LS MOSFETs are turned off. After a period of 20 soft start cycles, the IC attempts to re-start and goes through a soft start cycle. If the fault condition still exists, the above cycle will be repeated.

UVP is only active after the completion of soft-start sequence.

# **Output Over-Voltage Protection (OVP)**

For OVP implementation, output is monitored through FB pin. After soft start, if the voltage level at FB is above 0.96 V (typ.) ( $V_{OUT}$  is 120 % of  $V_{OUT}$  set point), OVP is triggered with both the HS and LS MOSFETs turned off. Normal operation is resumed once FB voltage drops back to 0.96 V.

OVP is active immediately after V<sub>CC</sub> passes UVLO level.

# **Over-Temperature Protection (OTP)**

SiC462 has internal thermal monitor block that turns off both HS and LS FETs when junction temperature is above 150 °C (typ). A hysteresis of 35 °C is implemented, so when junction temperature drops below 115 °C, the device restarts by initiating soft-start sequence again.

# Sequencing of Input / Output Supplies

SiC462 has no sequencing requirements on any of its input/output  $(V_{IN}, V_{DRV}, V_{DD}, V_{CIN}, EN)$  supplies or enables.

# Enable

The SiC462 has an enable pin to turn the part on and off. Driving this pin high enables the device, while grounding it turns it off.

The SiC462 enable has a weak pull down to prevent unwanted turn on due to a floating GPIO.

There are no sequencing requirements w.r.t other input/output supplies.

# Vishay Siliconix

#### Soft-Start

SiC462 soft-start time is adjustable by selecting a capacitor value from the following equation. Once  $V_{CC}$  is above UVLO level (2.55 V typ.),  $V_{OUT}$  will ramp up slowly, rising monotonically to the programmed output voltage. There is an internal 5  $\mu$ A current source tied to the soft start pin which charges the external soft start cap.

SS time =

$$\frac{C_{ext} \times 0.8 \text{ V}}{5 \mu A}$$

During soft-start period, OCP is activated. Short-circuit protection is not active until soft-start is complete.

# Pre-Bias Start-Up

In case of pre-bias startup, output is monitored through FB pin. If the sensed voltage on FB is higher than the internal reference ramp value, control logic prevents HS and LS FET from switching to avoid negative output voltage spike and excessive current sinking through LS FET.

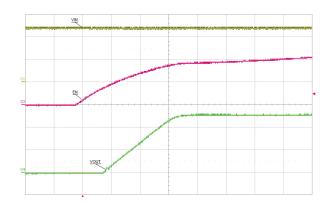

Fig. 7 - Pre-bias Start-up

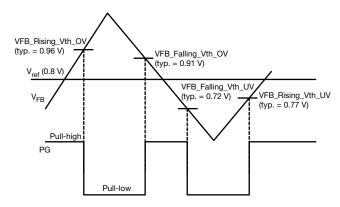

Fig. 8 - P<sub>GOOD</sub> Window and Timing Diagram

#### **Power Good**

SiC462's power good is an open-drain output. Pull  $P_{GOOD}$  pin high up to 5 V through a 10K resistor to use this signal. Power good window is shown in the diagram above. If voltage level on FB pin is out of this window, PG signal is de-asserted by pulling down to GND. To prevent false triggering during transient events,  $P_{GOOD}$  has a 25  $\mu s$  blanking time.

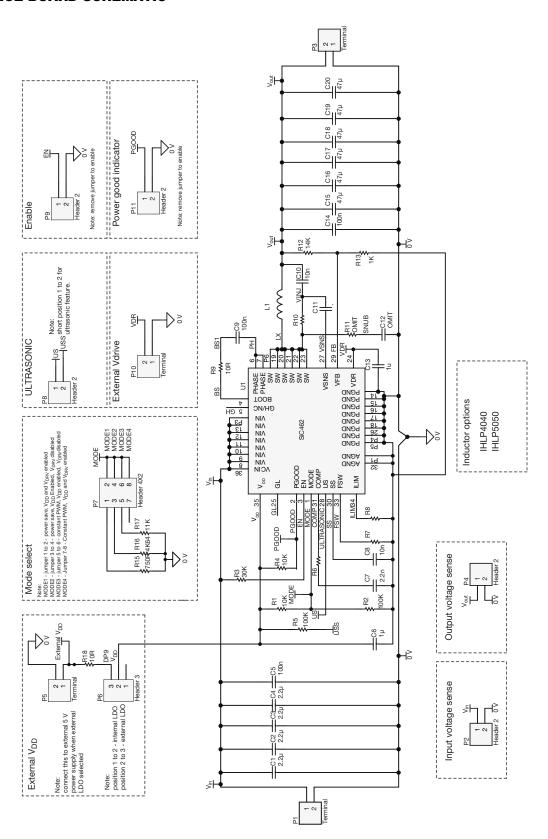

# **REFERENCE BOARD SCHEMATIC**

# Vishay Siliconix

| BILL | OF N | IATERIAL                                                                    |               |                                           |                     |                 |  |

|------|------|-----------------------------------------------------------------------------|---------------|-------------------------------------------|---------------------|-----------------|--|

| ITEM | QTY  | REFERENCE                                                                   | PCB FOOTPRINT | DESCRIPTION                               | PART NUMBER         | LIBREF          |  |

| 1    | 4    | C1, C2, C3, C4                                                              | 3216 (1206)   | 2.2 μF, 100 V<br>ceramic capacitor        | 12061C225KAT2A      | CAP2u2100V      |  |

| 2    | 3    | C5, C9, C14                                                                 | 1608 (0603)   | 100 nF, 100 V ceramic capacitor           | GRM188R72A104KA35D  | CAP100n100V     |  |

| 3    | 2    | C6, C13                                                                     | 1005 (0402)   | 1 μF, 6.3 V<br>ceramic capacitor          | 04026D105KAT2A      | CAP1u6.3V       |  |

| 4    | 2    | C7, C8                                                                      | 1005 (0402)   | Capacitor<br>(Semiconductor SIM<br>model) | Ceramic             | nic Cap Semi    |  |

| 5    | 1    | C10                                                                         | 1608 (0603)   | 10 nF, 100 V ceramic capacitor            | 06031C103KAT2A      | CAP10n100V_1_1  |  |

| 6    | 2    | C11, C12                                                                    | 1608 (0603)   | 1 nF, 100 V ceramic capacitor             | 06031C102KAT2A      | CAP1n100V       |  |

| 7    | 6    | C15, C16, C17,<br>C18, C19, C20                                             | 3216 (1206)   | 47 μF, 16 V<br>ceramic capacitor          | C3216C5R1C476M160AB | CAP47u16V       |  |

| 8    | 1    | L1                                                                          | IHLP-5050     | =                                         | Inductor            | B82559A0242A013 |  |

| 9    | 2    | P1, P3                                                                      | TERM2B        | Header, 2-pin                             | Terminal            | Header 2        |  |

| 10   | 5    | P2, P4, P8, P9, P11                                                         | HDR1X2        | Header, 2-pin                             | Header 2            | Header 2        |  |

| 11   | 2    | P5, P10                                                                     | TERM2         | Header, 2-pin                             | Terminal            | Header 2        |  |

| 12   | 1    | P6                                                                          | HDR1X3        | Header, 3-pin                             | Header 3            | Header 3        |  |

| 13   | 1    | P7                                                                          | HDR2X4        | Header, 4-pin, dual row                   | Header 4X2          | Header 4X2      |  |

| 14   | 16   | R1, R2, R3, R4, R5, R6,<br>R7, R8, R9, R10, R12,<br>R13, R15, R16, R17, R18 | 1005 (0402)   | Resistor                                  | Resistor Res1       |                 |  |

| 15   | 1    | R11                                                                         | 2012 (0805)   | Resistor                                  | Res1                | Res1            |  |

| 16   | 1    | U1                                                                          | MLP56-30L     | 55 V buck regulator                       | SiC462              | SiC462          |  |

#### **EXTERNAL COMPONENT SELECTION FOR THE SiC462**

A reference design has been developed to illustrate how to choose component values for proper operation of the SiC462. The schematic for the demo board is shown in Fig. 9 and Table 2.

#### **Demo Board Connection and Signal / Test Points**

#### **Power Sockets**

$V_{IN}$ , GND (P1): input voltage source with  $V_{IN}$  to be positive. Connect to a voltage source:

$V_{OUT}$ , GND (P3): output voltage with  $V_{OUT}$  to be positive. Connect to a load that draws no more than:

**5 V, GND (P10):** external 5 V MOSFET gate voltage source with 5 V to be the positive input. Apply 5 V when Mode 3 or Mode 4 is selected.

#### **Selection Jumpers**

#### **Mode Select**

**P7:** this is an 8 way header which allows the user to select one of four modes of operation.

MODE1 - SHORT PIN 1 to 2 Power save, V<sub>DRV</sub> and Pre-reg

MODE2 - SHORT PIN 3 to 4 Forced PWM,  $\textbf{V}_{DRV}$  and Pre-reg on

**MODE3 - SHORT PIN 5 to 6** Forced PWM, V<sub>DRV</sub> and Pre-reg off - external 5 V supply

**MODE4 - SHORT PIN 7 to 8** Power save, V<sub>DRV</sub> and Pre-reg off - external 5 V supply

#### **VDRV** External Supply

**P10:** this is a 2 way header that will enable the user to supply an external MOSFET gate driver supply if an external 5 V supply is available. This should only be used in MODES 3 and 4.

## **ENABLE**

**P9:** this is a 2 way header that will enable the part if left open. When shorted the part is disabled.

**OPEN Pin 1-2** - automatic enable on power up **SHORT Pin 1-2** - IC disabled.

#### **Ultrasonic**

**P8:** this is a 2 way header that will enable the user to select the ultrasonic mode of operation. In ultrasonic mode the minimum frequency of operation is 20 kHz, above the audible range. When not in ultrasonic mode the frequency can drop below 20 kHz.

**OPEN Pin 1-2** - ultrasonic disabled **SHORT Pin 1-2** - ultrasonic enabled

#### SIGNALS AND TEST LEADS

#### **Input Voltage Sense**

**V**<sub>IN\_SENSE</sub>, **GND**<sub>IN\_SENSE</sub> **(P2)**: this allows the user to measure the voltage at the input of the regulator and remove any losses generated due to the, connections from the measurement. This can also be used by a power source with sense capability.

## **Output Voltage Sense**

**V<sub>OUT\_SENSE</sub>**, **GND<sub>OUT\_SENSE</sub>** (P4): this allows the user to measure the voltage at the output of the regulator and remove any losses generated due to the connections, from the measurement. This can also be used by an active load with sense capability.

#### **POWER GOOD INDICATOR**

$P_{GOOD}$  (P11): is an open drain output and is pulled up with a 10 kΩ resistor to V<sub>IN</sub>. When FB or V<sub>OUT</sub> are within -10 % to +20 % of the set voltage this pin will go HI to indicate the output is okay.

#### POWER UP PROCEDURE

To turn-on the reference board, apply 12 V to  $V_{\text{IN}}$  with the P7 jumper is in position 1. If the P7 jumper is in place 1 the board will come up in power save mode, if in place 2 then constant PWM will be observed.

When applying higher than 12 V to the input it is reasonable to install a RC snubber from LX to GND if needed however this will affect efficiency. There are place holders on the reference board, R11 and C12 for the snubber. Values of 4  $\Omega$  and 1 nF are a reasonable starting point.

### ADJUSTMENTS TO THE REFERENCE BOARD

#### **OUTPUT VOLTAGE ADJUSTMENT**

If a different output voltage is needed, simply change the value of  $V_{\text{OUT}}$  and solve for R12 based on the following formula:

$$R_{12} = \frac{R_{13}(V_{OUT} - V_{FB})}{V_{FB}}$$

Where  $V_{FB}$  is 0.8 V for the SiC46X.  $R_{BOTTOM}$  (R13) should be a maximum of 10 k $\Omega$  to prevent  $V_{OUT}$  from drifting at no load.

# **CHANGING SWITCHING FREQUENCY**

The following equation illustrates the relationship between on-time,  $V_{\text{IN}}$ ,  $V_{\text{OUT}}$ , and  $R_{\text{fsw}}$  value:

$$R_{fsw} = R_7 = \frac{V_{OUT}}{f_{sw} \times 190e^{-12}}$$

# **OUTPUT RIPPLE VOLTAGE**

There is no requirement for this converter to see output capacitor ripple voltage in the control loop as a voltage injection circuit is employed; the voltage injection ramp is used to alert the converter to the next switch event.

Output ripple voltage is measured with a tip and barrel measurement across  $C_{OUT}$ ; the barrel of the probe is the GND / 0 V connection and this removes the effect of the long GND / 0 V leads of the probe. Typically output ripple voltage

# Vishay Siliconix

is set to 3 % to 5 % of the output voltage, but an all ceramic output solution can bring output ripple voltage to a much lower level since the ESR of ceramics can be in the range of  $m\Omega$ 's.

#### **VOLTAGE INJECTION NETWORK**

This is the network seen placed across the output inductor in the schematic consisting of R10, C10 and C11. A quick method to add or remove injection is to reduce or increase R10.

The time constant of the inductor,  $\tau IND$ , and voltage injection network are as follows:

$$\tau_{IND}\,=\,\frac{L}{DCR}$$

and

$$\tau_{INJ} = R_L \times C_L$$

In order to set a correct magnitude, the SiC46x requires around 100 mV, the following equation is used:

$$R_{L} = (V_{IN} - V_{OUT}) \times \left( \frac{V_{OUT}}{V_{OUT} \times f_{sw} \times C_{L} \times V_{INJECTION}} \right)$$

Where  $V_{\text{INJECTION}} = 100\text{mV}$  is the midpoint of the ripple injection RC circuit.

Fig. 9 - Voltage Injection Circuit

In fig. 1 the recommended value of CI = C10 (a or b)  $\approx$  2.2 nF and Cc = C11  $\approx$  22 nF.

The reference design allows placement of CI in two positions as shown in fig. 1, "a" and "b". The "b" option removes the output ripple and transient response voltage from the injection signal. The effect of connecting the CI capacitor to GND / 0 V is that some of the output information is removed from the fast loop however the output will be very stable in this setup when large transient loads are experienced at the output; in any case you will notice that the effective impedance of the output node is very small and the FB loop will react quickly enough for all loads. Another key aspect of using the GND / 0 V connection for the injection circuit is the ability to use a smaller output capacitance.

Be aware that the b) option is should only be used with forced PWM operation.

$$V_{INJ} = (V_{IN\_min.} - V_{OUT}) \times \left(1 - \frac{1}{\frac{t}{e^{\tau_{IN}}}}\right)$$

Where t is the ON period. The required magnitude is  $\sim 100 \text{ mVpp}$  for stable operation.

#### Compensation

The COT loop uses a transconductance amplifier to convert a proportional current from the output voltage,  $V_{FB}$ . This has the effect of offering a high impedance at the  $V_{FB}$  node, however this circuitry is left with a wide bandwidth to accommodate the different switching frequencies. This will require rolling off with an RC circuit, use the following equation:

$$R_{COMP} = \frac{\sqrt{L \times C_{OUT}}}{C_{COMP}}$$

C<sub>COMP</sub> will be set to 1 nF. This provides a frequency breakpoint around the LC filter peak. It may be necessary to reduce the roll off further, this can be a choice of the designer but an example might be to start at 1/2 the LC filter peak frequency. This will affect the transient response time, something to note is the minimal phase delay in the COT topology and its fast response compared to PWM converters.

#### INDUCTOR SELECTION

The choice of inductor is specific to each application and quickly determined with the following equations:

$$t_{ON} = \frac{V_{OUT}}{V_{IN \text{ max}} \times f_{sw}}$$

and

$$L = \frac{(V_{IN} - V_{OUT}) \times t_{ON}}{I_{OUT \text{ max}} \times K}$$

Where K is a percentage of maximum output current ripple required. The designer can quickly make a choice of inductor if the ripple percentage is decided, usually no more than 30 % however higher or lower percentages of I<sub>OUT</sub> can be acceptable depending on application. This device allows choices larger than 30 %.

Other than the inductance the DCR and saturation current parameters are key values. The DCR causes an  $I^2R$  loss which will decrease the system efficiency and generate heat. The saturation current has to be higher than the maximum output current plus 1/2 of the ripple current. In an over current condition the inductor current may be very high. All this needs to be considered when selecting the inductor.

On this board Vishay IHLP series inductors are used to meet cost requirement and high efficiency, a part that utilizes a material that has incredible saturation behaviour compared to competing products.

### **OUTPUT CAPACITOR SELECTION**

Voltage rating, ESR, transient response, overall PCB area and cost are requirements for selecting output capacitors. The types of capacitors and there general advantages and disadvantages are covered next.

Electrolytic have high ESR, dry out over time so ripple current rating must be examined and have slower transient response, but are fairly inexpensive for the amount of overall capacitance.

Tantalums can come in low ESR varieties and high capacitance value for its overall size, but they fail short when damaged and also have slower transient response.

Ceramics have very low ESR, fast transient response and overall small size, but come in low capacitance values compared to the others types. A combination of technology is sensible, however these converters suit an ceramic solution also.

The output capacitance will be determined by the ripple voltage requirement. Voltage mode COT topology can work with very small values of capacitor ESR.

The following equations are used to calculate the size needed to meet a transient load response:

$$I_{LPK} = I_{max.} + 0.5 \times I_{RIPPLE\ max.}$$

and

$$C_{OUT\_min.} = I_{LPK} \times \frac{L \times \frac{I_{LPK}}{V_{OUT}} - \frac{I_{max.}}{dI_{LOAD}} \times dt}{2 \times (V_{PK} - V_{OUT})}$$

Where  $I_{LPK}$  is the peak inductor current,  $I_{MAX}$  is the maximum output current,  $dI_{LOAD}$  is the current step in  $\mu$ s and  $V_{PK}$  is the peak voltage, the output voltage summed with the specified over and under shoot.

The evaluation PCB is fitter with 66 µF.

#### **ENABLE PIN VOLTAGE**

The EN pin has an internal pull down resistor and only requires an enable voltage. This needs to be greater than 1.4 V. An input voltage or a resistor connected across  $V_{IN}$  and EN can be used. The internal pull down resistance is  $5~\mathrm{M}\Omega$ .

#### SOFT START SETTING

Soft start is a useful function helping to limit the current magnitude from the source at switch on. This is simply set with a ceramic capacitor using the following equation:

$$t_{SS} = \frac{C_{SS} \times 0.8}{5e^{-6}}$$

A 100 nF capacitor will provide  $\sim$  16 ms soft start time.  $V_{DD}$  pin will need to be decoupled in order to provide a stable voltage internally and externally. The value for this capacitor is recommended as  $\geq$  1  $\mu$ F.

#### **CURRENT LIMIT RESISTOR**

The current limit is set by placing a resistor between pins LXS and I<sub>LIM</sub>. The values can be found using the following equation:

$$R_{ILIM} \, = \, \frac{480 \ 000}{I_{OUT\_max.}}$$

# **INPUT CAPACITANCE**

In order to keep the design compact and minimize parasitic elements, ceramic capacitors will be chosen. The initial requirement for the input capacitance is decided by the maximum input voltage, 60 V in this case however a 100 V rated capacitor will be chosen of the X7R variety. The footprint will be a compact 1206.

In order to determine the minimum capacitance the input voltage ripple needs to be specified;  $V_{CINPP} \leq 500$  mV is a suitable starting point. This magnitude is determined by the final application specification. The input current needs to be determined for the lowest operating input voltage,

$$I_{CIN(RMS)} = \frac{I_{OUT}}{V_{IN}} \times \sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}$$

The minimum input capacitance can then be found,

$$C_{IN\_min.} = I_{OUT} x \frac{DC - (1 - DC)}{V_{CINPKPK} x f_{sw}}$$

For output voltage greater than 5 V the input capacitance should be increased accordingly. As the output power increases so does the input voltage ripple, the evaluation PCB has  $4.4~\mu F$ .

### Note

If the input voltage becomes very small then extra capacitance needs adding to the input as the ripple will affect the duty cycle calculation when larger current is required.

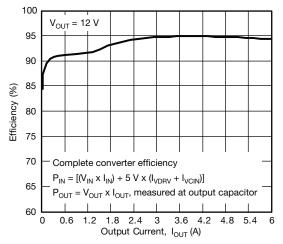

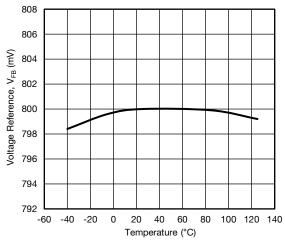

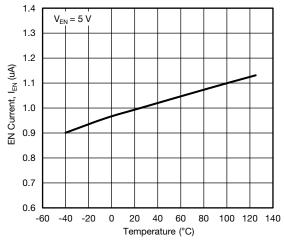

# **ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 48 \text{ V}$ , $V_{OUT} = 5 \text{ V}$ , $f_{sw} = 300 \text{ kHz}$ , $L = 15 \mu\text{H}$ , unless noted otherwise)

Fig. 10 - Efficiency vs. Output Current

Fig. 11 - On Resistance vs. Temperature

Fig. 12 - Voltage Reference vs. Junction Temperature

Fig. 13 - EN Current vs. Junction Temperature

Fig. 14 - EN Logic Threshold vs. Junction Temperature

Fig. 15 - Input Current vs. Input Voltage

# **ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 48 \text{ V}$ , $V_{OUT} = 5 \text{ V}$ , $f_{sw} = 300 \text{ kHz}$ , $L = 15 \mu\text{H}$ , unless noted otherwise)

Fig. 16 - Input Current vs. Junction Temperature

Fig. 17 - Shutdown Current vs. Input Voltage

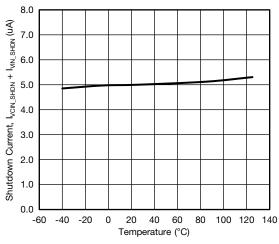

Fig. 18 - Shutdown Current vs. Junction Temperature

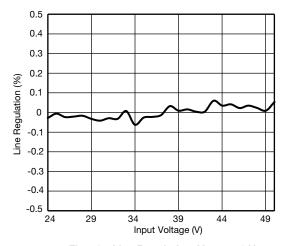

Fig. 19 - Line Regulation, V<sub>OUT</sub> = 12 V

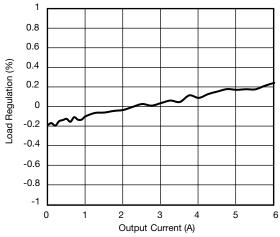

Fig. 20 - Load Regulation, V<sub>OUT</sub> = 12 V

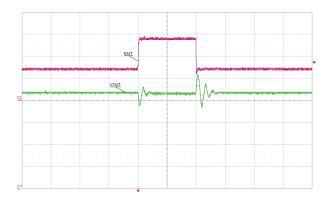

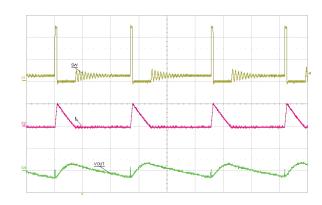

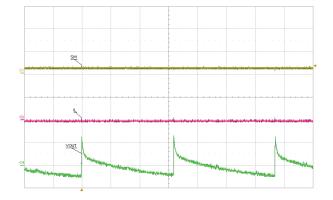

Fig. 21 - Load Transient - CH2 (RED) =  $I_{OUT}$  (2 A/div), CH4 (GREEN) =  $V_{OUT}$  (200 mV/div), Time = 100 µs/div

# **ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 48 \text{ V}$ , $V_{OUT} = 5 \text{ V}$ , $f_{sw} = 300 \text{ kHz}$ , $L = 15 \mu\text{H}$ , unless noted otherwise)

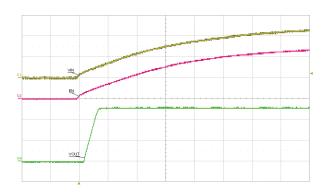

Fig. 22 - Load Line Transient (8 V to 48 V) - CH1 (YELLOW) =  $V_{IN}$  (20 V/div), CH3 (RED) = EN (5 V/div), CH4 (GREEN) =  $V_{OUT}$  (2 V/div), Time = 10 ms/div

Fig. 25 - Output Ripple 2 A - CH1 (YELLOW) = SW (20 V/div), CH2 (RED) =  $I_L$  (2 A/div), CH4 (GREEN) =  $V_{OUT}$  (20 mV/div), Time = 5  $\mu$ s/div

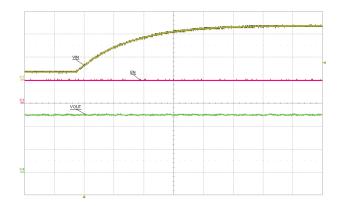

Fig. 23 - Start-Up with  $V_{IN}$  - CH1 (YELLOW) =  $V_{IN}$  (20 V/div), CH3 (RED) = EN (20 V/div), CH4 (GREEN) =  $V_{OUT}$  (2 V/div), Time = 5 ms/div

Fig. 26 - Output Ripple 300 mA - CH1 (YELLOW) = SW (20 V/div), CH2 (RED) =  $I_L$  (2 A/div), CH4 (GREEN) =  $V_{OUT}$  (50 mV/div), Time = 5  $\mu$ s/div

Fig. 24 - Start-Up with EN - CH1 (YELLOW) =  $V_{IN}$  (20 V/div), CH3 (RED) = EN (2 V/div), CH4 (GREEN) =  $V_{OUT}$  (2 V/div), Time = 1 ms/div

Fig. 27 - Output Ripple PSM - CH1 (YELLOW) = SW (20 V/div), CH2 (RED) =  $I_L$  (2 A/div), CH4 (GREEN) =  $V_{OUT}$  (20 mV/div), Time = 10 ms/div

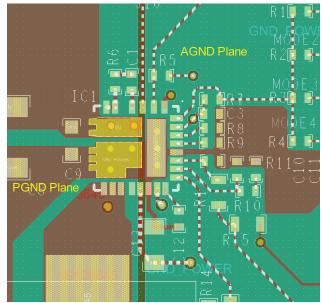

# **PCB LAYOUT RECOMMENDATIONS**

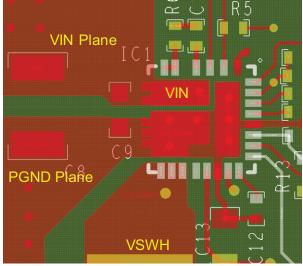

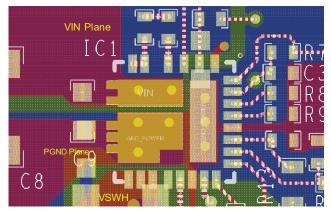

# Step 1: V<sub>IN</sub>/GND Planes and Decoupling

Fig. 28

- 1. Layout V<sub>IN</sub> and P<sub>GND</sub> planes as shown above.

- 2. Ceramic capacitors should be placed between  $V_{\text{IN}}$  and  $P_{\text{GND}}$ , and very close to the device for best decoupling effect.

- Different values / packages of ceramic capacitors should be used to cover entire decoupling spectrum e.g. 1210 and 0603.

- 4. Smaller capacitance values, placed closer to device's  $V_{\text{IN}}$  pin(s), is better for high frequency noise absorbing.

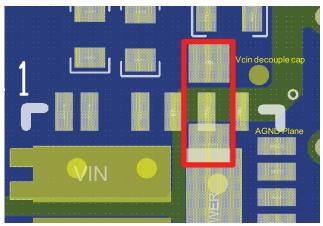

# Step 2: V<sub>CIN</sub> Pin

Fig. 29

- 1.  $V_{CIN}$  (pin 1) is the input pin for both internal LDO and  $t_{ON}$  block.  $T_{ON}$  time varies based on input voltage. It's necessary to put a decoupling capacitor close to this pin.

- 2. The connection can be made through a via and the cap can be placed at bottom layer.

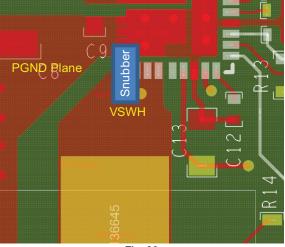

# Step 3: V<sub>SWH</sub> Plane

Fig. 30

- Connect output inductor to SiC462 with large plane to lower the resistance.

- 2. If any snubber network is required, place the components on the bottom side as shown above.

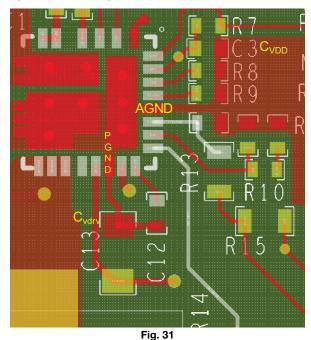

#### Step 4: V<sub>DD</sub>/V<sub>DRV</sub> Input Filter

ig. s i

- C<sub>VDD</sub> cap should be placed between pin 26 and pin 23 (the A<sub>GND</sub> of driver IC) to achieve best noise filtering.

- 2.  $C_{VDRV}$  cap should be placed close to  $V_{DRV}$  (pin 16) and  $P_{GND}$  (pin 17) to reduce effects of trace impedance and provide maximum instantaneous driver current for low side MOSFET during switching cycle.

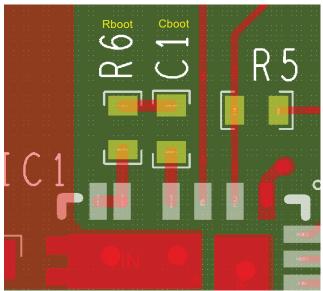

# Step 5: BOOT Resistor and Capacitor Placement

Fig. 32

- These components need to be placed very close to SiC462, right between PHASE (pin 5, 6) and BOOT (pin 4).

- 2. In order to reduce parasitic inductance, it is recommended to use 0402 chip size for the resistor and the capacitor.

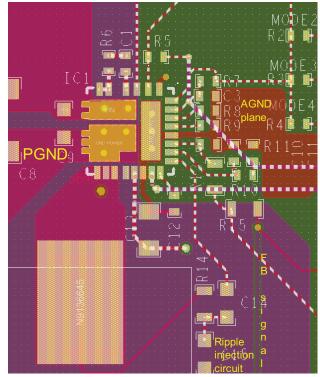

# Step 6: Signal Routing

Fig. 33

- 1. Separate the small analog signal from high current path. As shown above, the high current paths with high dv/dt, di/dt are placed on the left side of the IC, while the small control signals are placed on the right side of the IC. All the components for small analog signal should be placed closer to IC with minimum trace length.

- 2. Pin 23 is the IC analog ground, which should have a single connection to power ground. The  $A_{GND}$  ground plane connected with pin 23 helps keep  $A_{GND}$  quiet and improve noise immunity.

- 3. Feedback signal can be routed through inner layer. Make sure this signal is far away from  $V_{SWH}$  node and shielded by inner ground layer.

- Ripple injection circuit can be placed next to inductor. Kelvin connection as shown above is recommended.

# Vishay Siliconix

# Step 7: Adding Thermal Relief Vias and duplicate Power Path Plane

Fig. 34

- 1. Thermal relief vias can be added on the  $V_{\text{IN}}$  and  $P_{\text{GND}}$  pads to utilize inner layers for high-current and thermal dissipation.

- 2. To achieve better thermal performance, additional vias can be put on  $V_{\text{IN}}$  and  $P_{\text{GND}}$  plane. Also, it is necessary to duplicate the  $V_{\text{IN}}$  and ground planes at bottom layer to maximize the power dissipation capability from PCB.

- 3.  $V_{\text{SWH}}$  pad is a noise source and not recommended to put vias on this pad.

- 4. 8 mil drill for pads and 10 mils drill for plane are optional via sizes. The vias on pads may drain solder during assembly and cause assembly issues. Please consult with the assembly house for guidelines.

# Step 8: Ground Layer

Fig. 35

- 1. It is recommended to make the entire inner layer (next to top layer) ground plane.

- 2. This ground plane provides shielding between noise source on top layer and signal trace within inner layer.

- 3. The ground plane can be broken into two sections as  $P_{\mbox{\scriptsize GND}}$  and  $A_{\mbox{\scriptsize GND}}.$

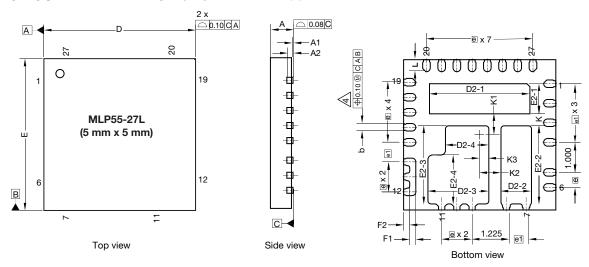

# PACKAGE OUTLINE DRAWING PowerPAK® MLP55-27

| DIM              | MILLIMETERS |           |      | INCHES    |            |       |  |

|------------------|-------------|-----------|------|-----------|------------|-------|--|

| DIM.             | MIN.        | NOM.      | MAX. | MIN.      | NOM.       | MAX.  |  |

| A <sup>(8)</sup> | 0.70        | 0.75      | 0.80 | 0.027     | 0.029      | 0.031 |  |

| A1               | 0.00        | -         | 0.05 | 0.000     | -          | 0.002 |  |

| A2               |             | 0.20 ref. |      |           | 0.008 ref. |       |  |

| b <sup>(4)</sup> | 0.20        | 0.25      | 0.30 | 0.078     | 0.098      | 0.011 |  |

| D                |             | 5.00 BSC  |      |           | 0.196 BSC  |       |  |

| е                |             | 0.50 BSC  |      |           | 0.019 BSC  |       |  |

| e1               |             | 0.65 BSC  |      |           | 0.0256 BSC |       |  |

| E                |             | 5.00 BSC  |      |           | 0.196 BSC  |       |  |

| L                | 0.35        | 0.40      | 0.45 | 0.014     | 0.016      | 0.018 |  |

| N (3)            |             | 28        |      |           | 28         |       |  |

| D2-1             | 3.25        | 3.30      | 3.35 | 0.128     | 0.130      | 0.132 |  |

| D2-2             | 0.95        | 1.00      | 1.05 | 0.037     | 0.039      | 0.041 |  |

| D2-3             | 1.95        | 2.00      | 2.05 | 0.077     | 0.079      | 0.081 |  |

| D2-4             | 1.37        | 1.42      | 1.47 | 0.054     | 0.056      | 0.058 |  |

| E2-1             | 0.95        | 1.00      | 1.05 | 0.037     | 0.039      | 0.041 |  |

| E2-2             | 2.55        | 2.60      | 2.65 | 0.100     | 0.102      | 0.104 |  |

| E2-3             | 2.55        | 2.60      | 2.65 | 0.100     | 0.102      | 0.104 |  |

| E2-4             | 1.58        | 1.63      | 1.68 | 0.062     | 0.064      | 0.066 |  |

| F1               | 0.20        | -         | 0.25 | 0.008     | -          | 0.010 |  |

| F2               | 0.20 min.   |           |      |           | 0.008 min. |       |  |

| K                | 0.40 BSC    |           |      | 0.016 BSC |            |       |  |

| K1               | 0.70 BSC    |           |      | 0.028 BSC |            |       |  |

| K2               | 0.70 BSC    |           |      | 0.028 BSC |            |       |  |

| K3               |             | 0.30 BSC  |      |           | 0.012 BSC  |       |  |

## Notes

- 1. Use millimeters as primary measurement

- 2. Dimensioning and tolerances conform to ASME Y14.5M 1994

- 3. N is the number of terminals, Nd is the number of terminals in x-direction, and Ne is the number of terminals in y-direction

- 4. Dimension b applies to plated terminal and is measured between 0.20 mm and 0.25 mm from terminal tip

- 5. The pin #1 identifier must be existed on the top surface of the package by using indentation mark or other feature of package body

- 6. Exact shape and size of this feature is optional

- 7. Package warpage max. 0.08 mm

- 8. Applied only for terminals

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?65124">www.vishay.com/ppg?65124</a>.